襯偏效應(yīng)(體效應(yīng))

對于MOS-IC而言,在工作時,其中各個MOSFET的襯底電位是時刻變化著的,若對器件襯底的電位不加以控制的話,那么就有可能會出現(xiàn)場感應(yīng)結(jié)以及源-襯底結(jié)出現(xiàn)正偏的現(xiàn)象;一旦發(fā)生這種現(xiàn)象時,器件和電路的溝道導(dǎo)電作用即告失效。

所以,對于IC中的MOSFET,需要在襯底與源區(qū)之間加上一個適當(dāng)高的反向電壓,以使得場感應(yīng)結(jié)始終保持為反偏狀態(tài),該所加的電壓就稱為襯偏電壓,這樣一來即可保證溝道始終能夠正常導(dǎo)電。簡言之,襯偏電壓就是為了防止MOSFET的場感應(yīng)結(jié)以及源結(jié)和漏結(jié)發(fā)生正偏、而加在源-襯底之間的反向電壓。

由于加上了襯偏電壓的緣故,即會引起若干影響器件性能的現(xiàn)象和問題,這就是襯偏效應(yīng)(襯偏調(diào)制效應(yīng)),又稱為MOSFET的體效應(yīng)。

MOS管體效應(yīng)(襯偏效應(yīng))分析

MOSFET 的體效應(yīng)(body-effect,也叫襯底調(diào)制效應(yīng)/襯偏效應(yīng)),主要是來源于 MOS 管的 S-B(Source-Bulk)端之間的偏壓對 MOSFET 閾值電壓 vth 的影響:

以 NMOS 的晶體管為例,當(dāng)晶體管的源端的電勢高于體端電勢時,源和體區(qū)的二極管反偏程度增加,柵下面的表面層中將有更多的空穴被吸引到襯底,使耗盡層中留下的不能移動的負(fù)離子增多,耗盡層寬度增加,耗盡層中的體電荷面密度 Qdep 也增加。

而從一般的 MOSFET 的閾值電壓的關(guān)系式中 Vth 與 Qdep 的關(guān)系(可以考率 Vth 為 MOS 柵電容提供電荷以對應(yīng)另一側(cè)耗盡區(qū)固定電荷的大小),可以看到閾值電壓將升高。

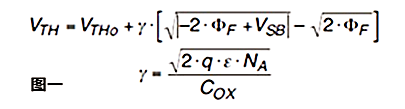

在考慮體效應(yīng)之后,MOS 管的閾值電壓可以寫為:

其中 γ 稱為體效應(yīng)因子, 通常與具體工藝相關(guān)。

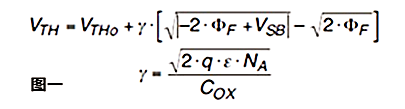

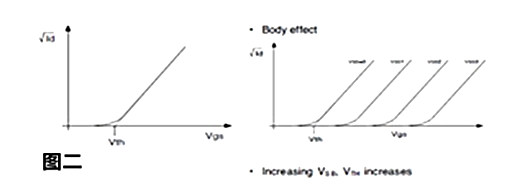

我們可以在圖二直觀的了解 VSB 對 Vth 的影響,隨著 VSB 電壓的增加,閾值電壓相應(yīng)的增大。

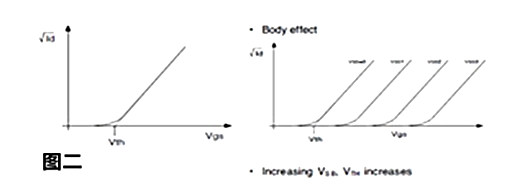

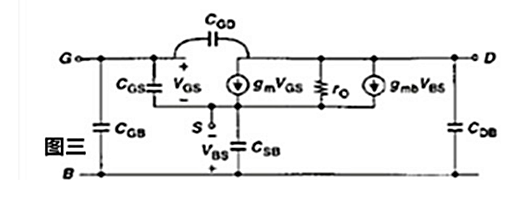

相應(yīng)的, 由于體效應(yīng)的存在, 在 MOSFET 的小信號模型中, 需要在 gm*VGS 的電流源旁并聯(lián)一個大小為 gmb*VBS 的電流源。

實際上,體效應(yīng)也可看成在 MOSFET 中存在由體端電壓控制的寄生的 JFET,若認(rèn)為 MOSFET 的柵電壓通過柵電容 Cox 控制溝道,則此 JFET 可以認(rèn)為是通過耗盡區(qū)電容 CD 來控制溝道的導(dǎo)電能力。

對于 N 阱工藝,由于阱區(qū)的摻雜濃度一般高于襯底的摻雜濃度,考慮到體效應(yīng)與雜質(zhì)濃度成正比(也可認(rèn)為 N-well 中有更大的耗盡層電容),因此 PMOS 相較 NMOS 有更顯著的體效應(yīng)。

一般可以將PMOS 的 N-well 和 S 端接一起以消除體效應(yīng)時,但此時需要注意 N-well 到襯底的電容的影響(這一電容在模型中可能不會考慮,一般可以假設(shè)電容大小為0.1fF/um^2 ) 確定是否影響電路中的信號通路。

襯偏效應(yīng)的影響:

1.閾值電壓升高

2.溝道電阻增大

3.產(chǎn)生背柵調(diào)制作用

4.產(chǎn)生襯底電容

5.輸出電阻降低

如何降低襯偏效應(yīng)的影響?

1、將源端與漏端短接。這也是采用的方法,如將NMOS的源漏都接地,將PMOS的源漏都接VDD。

2、改進(jìn)電路結(jié)構(gòu)。對于某些不能將源漏短接的情況,便只能在電路結(jié)構(gòu)層面上進(jìn)行改進(jìn)。如在CMOS中采用有源負(fù)載。

3、降低襯底的摻雜濃度,或者減小氧化層厚度(增強(qiáng)柵極的控制能力)。

4、源極和襯底短接。這可以完全消除襯偏效應(yīng)的影響,但是這需要電路和器件結(jié)構(gòu)以及制造工藝的支持,并不是在任何情況下都能夠做得到的。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經(jīng)理給您精準(zhǔn)的報價以及產(chǎn)品介紹

聯(lián)系號碼:18923864027(同微信)

QQ:709211280